Image and Signal Processing using Field Programmable

Gate Arrays

With the need for increased speed and integration, many real-time image and signal processing algorithms must be implemented in hardware. In the past this was through the design of dedicated processors. However, field programmable gate arrays (FPGAs) have matured to the stage where they now offer a practical and relatively inexpensive alternative to dedicated hardware. This project investigates aspects of mapping the algorithms for image processing and signal processing onto FPGAs.

Participating Staff

- Donald Bailey (Project Leader)

- Gourab Sen Gupta

Students

- Anoop Ambikumar (PhD: 2015-)

- Tariq Khan (Intern: 2014,2015) "Biometrics on FPGAs"

- Hitesh Rana (MEngStud: 2014-2015)

- Michael Klaiber (Intern: 2013) "High speed feature extraction using connected components"

- Miguel Contreras (ME: 2013-2016)

- Bram Bicknese (Intern: 2012) "Implementation of Smart-Camera Self-Calibration for Robot Soccer using Handel-C"

- Miguel Contreras (FYP: 2012) "FPGA Based Smart Camera for Robot Soccer"

- Ann De Silva (ME: 2011-2012) "Exploring the Implemenation of JPEG Compression of FPGA"

- Ni Ma (Intern: 2007) "Connected components labelling"

- Aaron Bishell (MSc: 2007-2008) "Designing Application Specific Processors for Image Processing"

- Andreas Buhler (ME: 2006-2007) "GateOS: A minimalist Windowing Environment and Operating System for FPGAs"

- Cameron Baker (FYP: 2005) "Interfacing FPGA to External Devices"

- Chris Johnston (PhD: 2004-2009) "VERTIPH: a visual environment for real-time image processing on hardware."

- Kim Gribbon (PhD: 2003-2010)

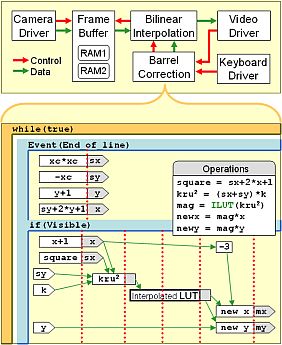

- Chris Johnston (FYP: 2003) "A Real-Rime FPGA Implementation of Barrel Distortion Correction Algorithm"

- David Johnson (FYP: 2002) "Hardware Implementation of Digital Signal Processing Algorithms"

Publications

- D. Bailey and A. Ambikumar, "Border handling for 2D transpose filter structures on an FPGA", Journal of Imaging, vol. 4, no. 12, pp. 138 (2018) [doi:10.3390/jimaging4120138].

- D.G. Bailey, Y. Chang, and S. Le Moan, "Lens distortion self-calibration using the Hough transform", in International Conference on Field Programmable Technology, Naha, Okinawa, Japan, (12-14 December, 2018) [doi:10.1109/FPT.2018.00080].

- J. Lues, G. Sen Gupta, and D. Bailey, "Evaluation of high-speed image processing for low latency control of a mechatronics system", in Robot Intelligence, Techniques and Applications (RiTA), Daejeon, Korea, (December 13-15, 2017). [doi:10.1007/978-3-319-78452-6_46]

- D. Bailey, "Hough transform line reconstruction on FPGA using back-projection", in International Conference on Field Programmable Technology (FPT), Melbourne, Australia, pp 283-286 (11-13 December, 2017). [doi:10.1109/FPT.2017.8280161]

- D. Bailey, "Streamed Hough transform and line reconstruction on FPGA", in Image and Vision Computing New Zealand (IVCNZ), Christchurch, New Zealand, (4-6 December, 2017). [doi:10.1109/IVCNZ.2017.8402473]

- D.G. Bailey, F. Mahmood, and U. Skoglund, "Reducing the cost of removing border artefacts in Fourier transforms", in International Symposium on Highly Efficient Accelerators and Reconfigurable Technologies (HEART 2017), Bochum, Germany, (7-9 June, 2017) [doi:10.1145/3120895.3120899].

- T.M. Khan, D.G. Bailey, M.A.U. Khan, and Y. Kong, "Efficient hardware implementation for fingerprint image enhancement using anisotropic Gaussian filter", IEEE Transactions on Image Processing, vol. 26, no. 5, pp. 2116-2126 (2017) [doi:10.1109/TIP.2017.2671781].

- D. Bailey and J.S.J. Li, "FPGA based multi-shell filter for hot pixel removal within colour filter array demosaicing", in Image and Vision Computing New Zealand (IVCNZ), Palmerston North, pp 196-201 (21-22 November, 2016) [doi:10.1109/IVCNZ.2016.7804450].

- M.J. Klaiber, D.G. Bailey, Y.O. Baroud, and S. Simon, "A resource-efficient hardware architecture for connected component analysis", IEEE Transactions on Circuits and Systems for Video Technology, vol. 26, no. 7, pp. 1334-1349 (2016) [doi:10.1109/TCSVT.2015.2450371].

- T.M. Khan, D.G. Bailey, M.A.U. Khan, and Y. Kong, "Efficient hardware implementation strategy for local normalization of fingerprint images", Journal of Real-Time Image Processing, pp. 13 pages (2016) [doi:10.1007/s11554-016-0625-8].

- M.J. Klaiber, D.G. Bailey, and S. Simon, "A single cycle parallel multi-slice connected components analysis hardware architecture", Journal of Real-Time Image Processing, pp. 1-11 (2016) [doi:10.1007/s11554-016-0610-2].

- D.G. Bailey, S. Randhawa, and J.S.J. Li, "Advanced Bayer demosaicing on FPGAs", in International Conference on Field Programmable Technology (FPT), Queenstown, NZ, pp 216-219 (7-9 December, 2015).

- D.G. Bailey, "Smart camera for Trax playing robot", in International Conference on Field Programmable Technology (FPT), Queenstown, NZ, pp 252-255 (7-9 December, 2015).

- D.G. Bailey, "The advantages and limitations of high level synthesis for FPGA based image processing", in International Conference on Distributed Smart Cameras, Seville, Spain, pp 134-139 (8-11 September, 2015).

- M.J. Klaiber, D.G. Bailey, Y.O. Baroud, and S. Simon, "A resource-efficient hardware architecture for connected component analysis", IEEE Transactions on Circuits and Systems for Video Technology, (2015)

- T.M. Khan, D.G. Bailey, M.A.U. Khan, and Y. Kong, "Real-time edge detection and range finding using FPGAs", Optik - International Journal for Light and Electron Optics, vol. 126, no. 17, pp. 1545-1550 (2015).

- G. Dessouky, M.J. Klaiber, D.G. Bailey, and S. Simon, "Adaptive dynamic on-chip memory management for FPGA-based reconfigurable architectures", in 24th International Conference on Field Programmable Logic and Applications (FPL), Munich, Germany, 8 pages (2-4 September, 2014).

- M. Contreras, D.G. Bailey, and G. Sen Gupta, "Techniques for designing an FPGA-based intelligent camera for robots", in 3rd International Conference on Robot Intelligence, Techniques, and Applications (RiTA 2014), Beijing, China, Advances in Intelligent Systems and Computing, AISC 345: 633-646 (6-8 November, 2014).

- M. Contreras, D. Bailey, and G. Sen Gupta, "Robot identification using shape features on an FPGA-based smart camera", in Image and Vision Computing New Zealand (ICVNZ), Hamilton, NZ, 294-299 (19-21 November, 2014).

- M. Contreras, D.G. Bailey, and G. Sen Gupta, "FPGA implementation of global vision for robot soccer as a smart camera", in 2nd International Conference on Robot Intelligence Technology and Applications, Denver, Colorado, USA, Advances in Intelligent Systems and Computing, 274: 657-665 (18-20 December, 2013).

- M.J. Klaiber, D.G. Bailey, S. Ahmed, Y. Baroud, and S. Simon, "A high-throughput FPGA architecture for parallel connected components analysis based on label reuse", in International Conference on Field Programmable Technology, Kyoto, Japan, pp 302-305 (9-11 December, 2013).

- D.G. Bailey and M. Klaiber, "Efficient hardware calculation of running statistics", in Image and Vision Computing New Zealand (IVCNZ), Wellington, NZ, pp 214-219 (27-29 November, 2013).

- D. Bailey, G. Sen Gupta and M. Contreras, "Intelligent camera for object identification and tracking", in 1st International Conference on Robot Intelligence Technology and Applications, Gwangju, Korea, (16-18 December, 2012).

- A.M. De Silva, D.G. Bailey, and A. Punchihewa, "Exploring the implementation of JPEG compression on FPGA", in 6th International Conference on Signal Processing and Communication Systems, Gold Coast, Australia, (12-14 December, 2012).

- D.G. Bailey, "Streamed high dynamic range imaging", in International Conference on Field Programmable Technology, Seoul, Korea, 305-308 (10-12 December, 2012).

- Bailey, D.G. (2012) "Implementing machine vision systems using FPGAs", in Machine Vision Handbook, B. Batchelor, Editor. Springer-Verlag London Limited, pp 1103-1136 [doi:10.1007/978-1-84996-169-1_25].

- Jongenelen, A.P.P., Bailey, D.G., Payne, A.D., Carnegie, D.A. and Dorrington, A.A. (2012) "Efficient FPGA implementation of homodyne-based time of flight range imaging", Journal of Real-Time Image Processing, vol. 7, no. 1, pp. 21-29 [doi:10.1007/s11554-010-0173-6].

- D. Bailey, M. Jones, and L. Tang, "Real time vision for measuring pipe erosion", in 5th International Conference on Automation, Robotics and Applications, Wellington, New Zealand, 486-491 (6-8 December, 2011).

- D. Bailey, "Considerations for hardware Hough transforms", in Image and Vision Computing New Zealand (IVCNZ), Auckland, NZ, 120-125 (29 November - 1 December, 2011).

- D. Bailey, "Invited paper: Adapting algorithms for hardware implementation", in 7th IEEE Workshop on Embedded Computer Vision, Colorado Springs, Colorado, USA, 177-184 (20 June, 2011).

- D.G. Bailey, "Design for Embedded Image Processing on FPGAs", John Wiley and Sons (Asia) Pte. Ltd. ISBN 978-0-470-82849-6

- A.P.P. Jongenelen, D.G. Bailey, A.D. Payne, A.A. Dorrington, and D.A. Carnegie, "Analysis of errors in ToF range imaging with dual-frequency modulation", IEEE Transactions on Instrumentation and Measurement, 60:(5) 1861-1868 (2011).

- D.G. Bailey, "Image border management for FPGA based filters", in 6th International Symposium on Electronic Design, Test and Applications, Queenstown, New Zealand, 144-149 (17-19 January, 2011).

- D.G. Bailey, "Efficient implementation of greyscale morphological filters", in International Conference on Field Programmable Technology (FPT 2010), Beijing, China, 421-424 (8-10 December, 2010).

- D.G. Bailey, "Chain coding streamed images through crack run-length encoding", in Image and Vision Computing New Zealand (IVCNZ 2010), Queenstown, New Zealand, 155-160 (8-9 November, 2010).

- C.T. Johnston, D. Bailey, and P. Lyons, "Notations for multiphase pipelines", in 5th IEEE International Symposium on Electronic Design, Test and Applications (DELTA 2010), Ho Chi Minh City, Vietnam, 212-216 (13-15 January, 2010).

- D. Bailey and C. Johnston, "Algorithm transformation for FPGA implementation", in 5th IEEE International Symposium on Electronic Design, Test and Applications (DELTA 2010), Ho Chi Minh City, Vietnam, 77-81 (13-15 January, 2010).

- D.G. Bailey and C.S. Bouganis, "Implementation of a foveal vision mapping", in International Conference on Field Programmable Technology (FPT'09), Sydney, Australia, 22-29 (9-11 December, 2009).

- D.G. Bailey and C.S. Bouganis, "Vision sensor with an active digital fovea", in Recent Advances in Sensing Technology. Springer-Verlag, LNEE 49: 91-111 (2009).

- C.T. Johnston, P. Lyons, and D. Bailey, "Paper based evaluation and overview of a visual language for real time image processing on FPGAs", in 10th International Conference of the NZ chapter of the ACM's Special Interest Group on Human-Computer Interaction (CHINZ 2009), Auckland, NZ, 85-92 (6-7 July, 2009).

- D.G. Bailey and C.-S. Bouganis, "Tracking performance of a foveated vision system", in International Conference on Autonomous Robots and Agents (ICARA 2009), Wellington, NZ, 414-419 (10-12 February, 2009).

- N. Ma, D. Bailey, and C. Johnston, "Optimised single pass connected components analysis", in International Conference on Field Programmable Technology, Taipei, Taiwan, 185-191 (8-10 December, 2008).

- D. Bailey and C.S. Bouganis, "Reconfigurable foveated active vision system", in International Conference on Sensing Technology, Tainan, Taiwan, 162-169 (30 November - 3 December, 2008).

- D.G. Bailey, C.T. Johnston, and N. Ma, "Connected components analysis of streamed images", in International Conference on Field Programmable Logic and Applications, Heidelberg, Germany, 679-682 (8-10 September, 2008).

- C.T. Johnston, P. Lyons, and D.G. Bailey, "A Visual Notation for Processor and Resource Scheduling", in IEEE International Symposium on Electronic Design, Test and Applications (DELTA 2008), Hong Kong, pp 296-301 (23-25 January, 2008).

- C.T. Johnston and D.G. Bailey, "FPGA implementation of a Single Pass Connected Components Algorithm", in IEEE International Symposium on Electronic Design, Test and Applications (DELTA 2008), Hong Kong, pp 228-231 (23-25 January, 2008).

- D.G. Bailey and C.T. Johnston, "Single Pass Connected Components Analysis", in Image and Vision Computing New Zealand, Hamilton, New Zealand, pp 282-287 (5-7 December, 2007).

- K.T. Gribbon, D.G. Bailey, and A. Bainbridge-Smith, "Development Issues in Using FPGAs for Image Processing", in Image and Vision Computing New Zealand, Hamilton, New Zealand, pp 217-222 (5-7 December, 2007).

- A.D. Bishell, D.G. Bailey, and P. Lyons, "Designing Custom Processors on FPGAs for Specific Applications", in Electronics New Zealand Conference, Wellington, NZ, pp 7-12 (12-13 November, 2007).

- D.G. Bailey, "Space Efficient Division on FPGAs", in Electronics New Zealand Conference (EnzCon'06), Christchurch, NZ, pp 206-211 (13-14 November, 2006).

- C.T. Johnston, D.G. Bailey, and P. Lyons, "A Visual Environment for Real Time Image Processing in Hardware (VERTIPH)", EURASIP Journal on Embedded Systems, 2006:(Article ID 72962) 8 pages (2006)

- C.T. Johnston, D.G. Bailey, and P. Lyons, "Towards a Visual Notation for Pipelining in a Visual Programming Language for Programming FPGAs", in 7th International Conference of the NZ chapter of the ACM's Special Interest Group on Human-Computer Interaction (CHINZ 2006), Christchurch, NZ, ACM International Conference Proceeding Series, 158: 1-9 (July 6-7, 2006).

- K.T. Gribbon, C.T. Johnston, D.G. Bailey, "Formalizing Design Patterns for Image Processing Algorithm Development on FPGAs", Proceedings of the third IEEE International Workshop on Electronic Design, Test, and Applications (Delta 2006), Kuala Lumpur, Malaysia, pp 47-53 (17-19 January, 2006)

- Donald Bailey, Kim Gribbon, Chris Johnston, "GATOS: A Windowing Operating System for FPGAs", Proceedings of the third IEEE International Workshop on Electronic Design, Test, and Applications (Delta 2006), Kuala Lumpur, Malaysia, pp 405-409, (17-19 January, 2006)

- C.P. Baker, D.G. Bailey, "Interfacing hardware to FPGAs", Projects Journal, 14, pp 1-5 (2005)

- C.T. Johnston, D.G. Bailey, K.T. Gribbon, "Optimisation of a colour segmentation and tracking for real-time FPGA implementation", Image and Vision Computing New Zealand, Dunedin, pp 422-427 (28-29 November, 2005)

- Christopher T. Johnston, Kim T. Gribbon, Donald G. Bailey, "FPGA Based Remote Object Tracking for Real-time Control", International Conference on Sensing Technology, Palmerston North, pp 66-71 (21-23 November 2005)

- K.T. Gribbon, C.T. Johnston, D.G. Bailey, "Formalizing Design Patterns for Image Processing Algorithm Development on FPGAs", IEEE Tencon'05, Melbourne, Australia, (21-24 November 2005)

- K. Gribbon, D.G.Bailey, C.T. Johnston, "Colour edge enhancement", Proceedings Image and Vision Computing New Zealand 2004, Akaroa, New Zealand, pp 291-296 (November 2004)

- C.T. Johnston, D.G.Bailey, P. Lyons, K.T. Gribbon, "Formalisation of a Visual Environment for Real Time Image Processing in Hardware (VERTIPH)", Proceedings Image and Vision Computing New Zealand 2004, Akaroa, New Zealand, pp 297-302 (November 2004)

- C.T. Johnston, K.T. Gribbon, D.G. Bailey, "Implementing Image Processing Algorithms on FPGAs", Proceedings of the Eleventh Electronics New Zealand Conference, ENZCon'04, Palmerston North, New Zealand, pp 118-123 (November 2004)

- K.T. Gribbon, D.G. Bailey, "A Novel Approach to Real Time Bilinear Interpolation", Proceedings of the IEEE International Workshop on Electronic Design, Test, and Applications, Perth, Australia, pp 126-131 (January 2004).

- C.T. Johnston, D.G. Bailey, "A Real-time FPGA Implementation of a Barrel Distortion Correction Algorithm", Projects Journal, 12: 91-96 (2003)

- K.T. Gribbon, C.T. Johnston, D.G. Bailey, "A Real-time FPGA Implementation of a Barrel Distortion Correction Algorithm with Bilinear Interpolation", Proceedings of Image and Vision Computing New Zealand, Palmerston North, New Zealand, pp 408-413 (November 2003).

- D.J. Johnson, D.G. Bailey, S.N. Demidenko, "Hardware Implementation of Digital Signal Processing Algorithms", Projects Journal, 11: 104-109 (2002).

- D Johnson, K. Gribbon, D Bailey, and S. Demidenko, "Implementing Signal Processing Algorithms in FPGAs: Digital Spectral Warping", in Ninth Electronics New Zealand Conference (ENZCon'02), Dunedin, New Zealand, 72-77 (14-15 November, 2002).